名家芯思维——FPGA助力人工智能|第68期国际名家讲堂

一、活动安排

1.名家芯思维

2018年FPGA助力人工智能研讨会

(免费参与)

活动时间:2018年7月24日(周二上午)

活动地点:南京江北新区产业技术研创园

(南京浦口区团结路99号孵鹰大厦A座3楼316)

临江路地铁1号口有免费接驳车送至研创园

2.第68期国际名家讲堂

FPGA时序/功耗优化和软硬件协同设计

(需注册费,详见下文)

活动时间:2018年7月24-26日(周二-周四2.5天)

活动地点:南京江北新区智芯科技楼7楼

(南京江北新区星火路15号)

南京地铁3号线星火路地铁站1号或4号出口100米

一、名家芯思维

2018年FPGA助力人工智能研讨会

(免费参与)

活动时间:2018年7月24日(周二上午)

活动主题:FPGA助力人工智能

活动地点:南京江北新区产业技术研创园

(南京市浦口区团结路99号孵鹰大厦A座3楼316)

活动议程:

报名方式

1.邮件报名

报名回执表下载链接:http://www.icplatform.cn/form

填写报名回执表并发送Word电子版至“芯动力人才计划”邮箱:icplatform@miitec.cn,

邮件题目格式:报名+FPGA助力人工智能研讨会+单位名称+人数;

邮件内容:含有姓名、单位、部门及职务、电话、邮箱。

2.微信报名

扫一扫下方二维码,直接报名(推荐)

3.电话报名

汪晨 025-69640094 13901584204

张欢 025-69678210 18262610717

二、第68期国际名家讲堂

(FPGA时序/功耗优化和软硬件协同设计)

讲堂+实操

专家介绍

哈亚军

Yajun Ha

上海科技大学教授

个人履历:

1996年获浙江大学学士学位。

1999年获新加坡国立大学硕士学位。

2004年获比利时鲁汶大学博士学位。

目前是上海科技大学的全职教授。之前,他是担任新加坡资讯与通信研究院科学家及比亚迪联合实验室主任。同时,他还是新加坡国立大学电子与计算机工程系的副教授。

曾在比利时欧洲微电子中心(IMEC) 任研究员,在上海航天局航天测控通信研究所参加研究工作。

研究领域:

FPGA的架构、工具和应用、可重构计算、低功耗数字集成电路与系统设计、机器人与智能车以及和智能硬件相关的嵌入式系统研究及应用。

所在机构及协会任职:

2016-2017年,担任IEEE电路和系统I(TCASI)杂志的副主编;

2013-2014年,担任IEEE超大规模集成系统(TVLSI)杂志的副主编;

2011-2013年,担任IEEE电路和系统II(TCASII)杂志的副主编;

2009年以来,担任低功耗电子(JOLPE)杂志的副主编。

担任亚太电子设计自动化会议(ASP-DAC)2014年组委会主席;可编程技术国际会议FPT 2010和FPT 2013技术委员会主席;IEEE电路和系统协会新加坡分会主席(2011年和2012年);ASP-DAC指导委员会成员;以及IEEE CAS VLSI和应用技术委员会成员。

他是嵌入式系统和FPGA领域的许多知名会议的技术委员会成员,如DAC、DATE、ASP-DAC、FPGA、FPL和FPT。他是上海“千人计划”学者。他也是IEEE的高级成员。

所获荣誉:

在TCAS I & II 、TVLSI、TC、JSSC以及DAC和ISSCC等国际知名期刊和会议上发表了近百篇学术论文。

讲堂大纲

1.FPGAs: Overview of architectures and tools

FPGAs: 架构和工具的概述

本部分将从回顾数字系统设计基础开始,为本课程的其他主题奠定基础。在同步设计中,设计准则、时间和功耗约束将被强调,因为它们是所有FPGA设计应该遵循的初始要求。接下来,我们将概述一般的FPGA架构和工具,并用供应商提供的FPGA架构和工具的实例来说明。

具体的主题包括:

Digital system design basics 数字系统设计的基础

Overview of FPGA architectures FPGA架构的概述

Overview of FPGA design tools FPGA设计工具的概述

这堂课也将介绍课程的整体内容,并解释将会遵循的逻辑与方法。重要的是,课程的主要学习目标将会被阐释,以及为完成这些目标所需要做的事。

2.Timing Concepts 时间概念

满足时间要求通常是FPGA实现最重要的挑战,特别是当所需的时钟频率很高时。我们讨论了数字电路和系统中使用的各种计时概念,并说明了时间限制,它们来自哪里,以及它们如何帮助改进FPGA实现的计时性能。我们将在相应的实操中加强对概念的理解。

本节的具体主题包括:

Synchronous vs. asynchronous circuits 同步vs. 非同步电路

Synchronous timing concepts 同步时序概念

Global timing constraints 全局时序限制

Specific timing constraints 具体时序约束

Timing simulation 时序仿真

Timing report 时序报告

The corresponding lab will be: 相应的实验练习为:

Lab 1: Understanding Timing Simulation and Report

实验一: 了解时序模拟和报告

3.FPGA Timing Closure Techniques FPGA时序闭合技术

根据前一部分讨论的概念,本部分将推荐高级FPGA体系结构中所选的组件,这些组件可能有助于改进时间安排。例如,各种定时验证的IP硬核、高质量的时钟管理器等等。此外,为了支持FPGAs进出数据传输需求的不断增长,FPGAs中加入了高速I/O模块,如多千兆收发机和以太网IP核。讨论了高速度FPGA电路的高密度编码技术。最后总结了一种快速高速时序闭合的推荐设计流程。

具体的主题包括:

Timing proven IP hard cores 时序已被验证的IP硬核

Using high quality clocking 使用高质量的时钟

Using high speed I/O modules 使用高速I / O模块

HDL coding techniques for high speed circuits HDL编码技术

High speed timing closure design flow 高速时序闭合设计流程

The corresponding lab will be: 相应的实操为:

Lab 2: Timing Optimization for Closure

实验二: 时序闭合优化

4.Power Concepts 功耗概念

在移动应用中,由于FPGA实现的功耗限制了每次电池充电后的工作时间,因此满足功耗通常是FPGA实现的关键挑战。我们将讨论数字电路和系统中使用的各种电源概念,并展示什么是电源组件,它们来自哪里,以及如何评估FPGA实现的功耗。我们将在相应的实验中加强对概念的理解。

具体的主题包括:

FPGA power consumption components ·FPGA功耗来源

Low power FPGA architectures ·低功耗FPGA架构

Low power FPGA design tools & algorithms 低功耗FPGA设计工具和算法

FPGA power estimation FPGA功率估计

The corresponding lab will be: 相应的实操为:

Lab 3: FPGA Power Evaluation

实验三:FPGA功耗评估

5.FPGA Power Optimization Techniques FPGA功耗优化技术

基于前一部分讨论的概念,本部分将讨论实现低功耗FPGA实现的一些功耗优化技术,以及使用FPGA设计工具实现低功耗的正确设计方法。

具体的主题包括:

FPGA power optimization techniques FPGA功耗优化技术

Low power design guidelines 低功耗设计指导方针

The corresponding lab will be: 相应的实操为:

Lab 4: FPGA Power Optimization

实验四: FPGA功耗优化

6.Processor and Accelerator Based Computing Architecture

基于处理器和加速器的计算体系结构

在FPGA计算系统中,我们通常将计算非密集型代码分配给处理器(PS),而计算密集型代码分配给基于FPGA逻辑(PL)的加速器。本部分主要介绍处理器+加速器(PS+PL)体系结构的主要概念。主题包括I/O接口、寻址、中断、直接内存访问等。

7.Software/Hardware Co-Design Flow 软件/硬件协同设计流程

本部分介绍了如何使用SDSoC框架进行软硬件协同设计。我们首先讨论如何构建SDSoC联合设计平台,该平台由PS+PL硬件体系结构及其Linux OS系统软件组成。然后介绍了如何在PS上编译算法。第三,我们讨论了如何使用剖析来分析算法,知道算法的哪一部分应该分配给PS,哪一部分应该分配给PL。最后,我们使用SDSoC来帮助我们快速实现所决定的软硬件划分,并对其性能进行评估。

The corresponding lab will be: 相应的实操为:

Lab 5: Software/Hardware Co-Design with SDSoC

实验五: 软件/硬件与SDSoC协同设计

8.Software/Hardware System Optimization 软件/硬件系统的优化

讨论了软硬件协同设计系统的优化问题。利用前一部分得到的共同设计的系统,我们可能想进一步提高系统性能。我们将讨论如何使用高级合成工具来优化这方面的PL硬件性能。

The corresponding labs will be: 相应的实操为:

Lab 6: Co-Design Optimization

实验六: 协同设计优化

Lab 7: Building SDSoC Co-Design Platform

实验七: 搭建SDSoC协同设计平台

注册费用

(1)注册费用:4800元/期

在线报名请选择“普通学员注册”通道

(2)芯动力合作单位学员:3800元/期

在线报名请选择“合作单位学员注册”通道

(3)学生福利:

全国高校学生(本硕博)参加国际名家讲堂,享受标准注册费半价福利;

南京本地学校学生专享注册费:1000元/人。

在线报名请选择“学生注册”通道

(4)老学员福利:

凡已付费参加任意一期2018年国际名家讲堂,均可本人以半价注册费参加后续6个月内任意一期2018年国际名家讲堂。

在线报名请选择“老学员注册”通道

(5)高校福利:

全国高校教师(付费注册)可免费携带1名学生

教师在线报名请选择“普通学员注册”通道,携带的学生请选择“特邀注册”通道

注:

①优惠政策:针对学员推出Bonus Class IV优惠政策,详情请点击蓝字部分。

②学生注册费,需提供学生证或所在学校出具的学生证明(加盖学校或学院公章),扫描件发送至邮箱:icplatform@miitec.cn,审核通过后即可参加。

③含授课费、资料费、活动期间午餐。不含学员交通、住宿等费用(学员自理)。

国信芯世纪南京信息科技有限公司为本期国际名家讲堂开具发票,发票内容为培训费。

请于2018年7月20日前将注册费汇至以下账户,并在汇款备注中注明款项信息(第68期+单位+参会人姓名)。

付款信息:

户 名:国信芯世纪南京信息科技有限公司

开户行:中国工商银行股份有限公司南京浦珠路支行

帐 号:4301014509100090749

或请携带银行卡至活动现场,现场支持 POS 机付款。

报名方式

1.邮件报名(推荐)

报名回执表下载链接:http://www.icplatform.cn/form

填写报名回执表并发送Word电子版至“芯动力人才计划”邮箱,邮箱地址:icplatform@miitec.cn

回执表文件名和邮件题目格式为:“报名+第68期+单位名称+人数”。

2.微信报名

扫描下方二维码,在线报名(推荐):

报名须知:本次活动,采取线上报名,线下付款的形式,线下付款可以对公打款,或者现场POS刷卡付款,请在线提交报名!

3.电话报名

汪晨 025-69640094 13901584204

张欢025-69678210 18262610717

住宿预订

酒店名称:南京新逸天金丝利酒店

酒店地址:南京市浦口区丽景路8号(地铁三号线东大成贤学院4号出口400米)

协议价格:豪华单人间/标准间 338元/间

预定方式:请需要预订酒店的学员在7月20 日12点前联系工作人员。

预定酒店联系人:

郁大鹏 18017813372

邮箱:icqy@miitec.cn

交通路线

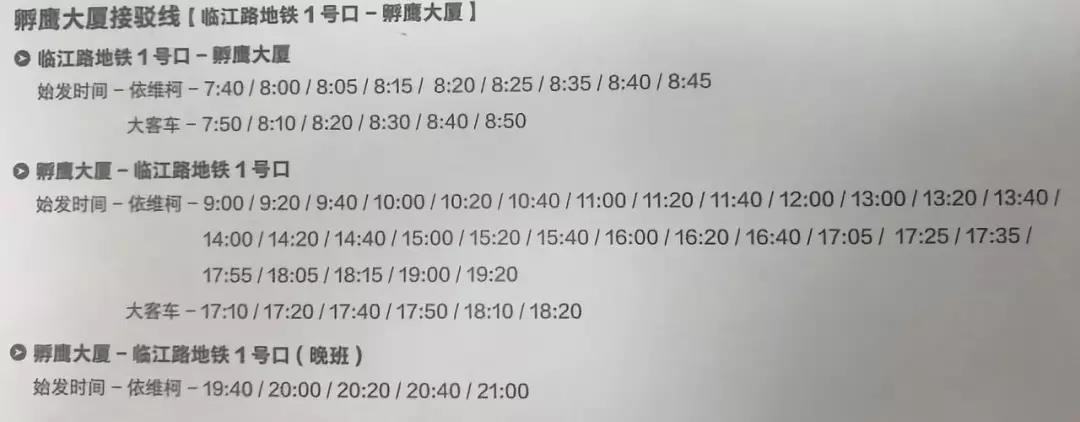

1、名家芯思维:南京市江北新区产业技术研创园

接驳车线路时间如下(地铁10号线临江路1号口有免费接驳车送至研创园)

2、第68期国际名家讲堂:南京市江北新区智芯科技楼7楼

路线:南京地铁3号线星火路地铁站1号口南100米

2017年FPGA研讨会及讲堂现场集锦

2017年9月20日,由工业和信息化部人才交流中心(MIITEC)和比利时微电子研究中心(IMEC)联合主办的“名家芯思维”之2017年FPGA产业及应用研讨会在江苏省南通市成功举办,200余人参加本次活动。清华大学魏少军教授,无锡中微亿芯有限公司总经理单悦尔,赛灵思公司(Xilinx)研究院前沿技术拓展经理 陆佳华,中国科学院杨海钢教授、可编程芯片与系统研究室主任杨海钢分别进行主题分享。

9月20—22日,“芯动力”人才发展计划——国际名家讲堂第46期“FPGA架构,工具和应用”在南通举办。上海科技大学哈亚军教授与学员们交流探讨FPGA架构、工具和应用的相关内容。本次活动130余位来自企业、高校、科研院所的技术研究人员、相关代表前来参加。

哈教授围绕“FPGA架构,工具和应用”的主题,从理论技术、应用分享等多个不同的角度深入分析FPGA的架构、工具和应用。

哈亚军教授指出FPGA架构使数字系统得以运用,一般有三部分组成:可编程化逻辑,可编程化路径和可编程化I/O;讨论了FPGA架构中每个组成的作用,并且说明FPGA架构空间的系数,并展示多年来如何发展和改良。此外,聚焦于通用的FPGA架构,提供来自主要FPGA供应商的FPGA架构实例:如Xilinx 和 Altera。

同时,讲堂中论述进阶的FPGA架构主题。如为支持FPGA中的数据转换的增长性需求,FPGA中加入了高速输入、输出系统,例如千兆级收发器和以太网IP核。论述了在新的FPGA架构中低能耗和高速度I/O,最终比较不同应用中使用FPGA和ASIC为计算平台。

FPGA应用部分介绍了包括国防航空航天电子设备,医疗电子,汽车影像,实况影像引擎,消费电子,数字显示,数据中心服务器,高性能计算服务器,工业成像,医疗超声波,影像及图像处理高清摄影,有线通信,光传输网络,无线通信处理器等方面的应用。哈教授运用应用及案例剖析FPGA的技术内容和相关应用,使学员们对“FPGA”的相关技术及其应用有了更加全面的了解。

芯动力人才计划介绍

“芯动力”人才计划是工业和信息化部人才交流中心设立的服务国家集成电路产业发展的人才专项,通过整合国内外优质智力资源,搭建园区、企业、专家、人才等行业要素广泛参与、资源共享的交流平台,构建充满活力和富含价值的集成电路产业人文生态环境。

“IC智慧谷”是“芯动力”人才计划的重要组成部分,以提升城市产业品牌、实现集成电路产业人才和项目集聚为目标,由中心与地方政府共同运营。